# INTEGRATED CIRCUITS

# Semiconductors for Radio and Audio Systems

1997

**Data Handbook IC01**

Let's make things better.

**PHILIPS**

#### **QUALITY ASSURED**

Our quality system focuses on the continuing high quality of our components and the best possible service for our customers. We have a three-sided quality strategy: we apply a system of total quality control and assurance; we operate customer-oriented dynamic improvement programmes; and we promote a partnering relationship with our customers and suppliers.

#### PRODUCT SAFETY

In striving for state-of-the-art perfection, we continuously improve components and processes with respect to environmental demands. Our components offer no hazard to the environment in normal use when operated or stored within the limits specified in the data sheet.

Some components unavoidably contain substances that, if exposed by accident or misuse, are potentially hazardous to health. Users of these components are informed of the danger by warning notices in the data sheets supporting the components. Where necessary the warning notices also indicate safety precautions to be taken and disposal instructions to be followed. Obviously users of these components, in general the set-making industry, assume responsibility towards the consumer with respect to safety matters and environmental demands.

All used or obsolete components should be disposed of according to the regulations applying at the disposal location. Depending on the location, electronic components are considered to be 'chemical', 'special' or sometimes 'industrial' waste. Disposal as domestic waste is usually not permitted.

# Semiconductors for Radio and Audio Systems

DATA HANDBOOK SYSTEM

GENERAL

|              |      |  | Page |

|--------------|------|--|------|

| PREFACE      |      |  | 3    |

| SELECTION GL | IIDE |  | 5    |

**CONTENTS**

17

405

| DEVICE DATA |  |      | 27 |

|-------------|--|------|----|

|             |  | - 24 |    |

#### **DEFINITIONS**

| Data sheet status         |                                                                                                                                                                               |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | This data sheet contains target or goal specifications for product development.                                                                                               |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later.                                                                                         |

| Product specification     | This data sheet contains final product specifications.                                                                                                                        |

| Short-form specification  | The data in this specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook |

#### Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### Application information

Where application information is given, it is advisory and does not form part of the specification.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

#### PURCHASE OF PHILIPS I2C COMPONENTS

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specification defined by Philips. This specification can be ordered using the code 9398 393 40011.

#### **PREFACE**

The audio/video market is characterized by a continuing demand for innovation to increase the functionality of ICs by achieving ever higher levels of integration, reducing power consumption, minimizing the number of peripheral components and reducing the need for circuit alignment during assembly. We achieve these goals by extensive use of computer control via the I2C-bus, and by designing analog, digital and mixed signal circuits using the very latest signal processing techniques. We then fabricate the ICs with state-of-the-art production processes so we can offer you complete `systems-on-silicon' which help you maintain your competitive edge by staying one step ahead of the competition.

#### An innovative and reliable supplier

A total systems approach, embracing both hardware and software, is the foundation on which we have built our unrivalled reputation as an innovative and reliable supplier of high quality semiconductors for the audio/video segments of the consumer electronics market.

Our strengths in this field stem not only from being a large multinational organization with the resources to stay the course, but also from our dedication to research and to forming true and lasting partnerships with our customers.

# World-class manufacturing, resources and customer support

Philips Semiconductors is a global supplier. We employ some 20,000 people, have more than 100 sales offices worldwide, are represented in 44 countries, and manufacture over 14,000 different products. Philips also has a level of commitment to research matched by very few companies, not just in terms of resources but in their focus on researching solutions for customers. Philips Semiconductors collaborates very closely with Philips Corporate Research Laboratories, one of the largest privately funded research organisations in the world. Five major research laboratories serve the whole group, in the Netherlands, UK, France, Germany and the USA.

As you would expect from a worldwide organization, our support doesn't end with the timely delivery of ICs and discretes to our audio/video customers. We are also dedicated to the aim of zero-defects quality for our semiconductors, and to offering unequalled service. There are Philips customer support and application centres in every major market area (Europe, Asia-Pacific, North America) to ensure that you can take full advantage of our extensive applications know-how and broad product range. Four Product Concept and Applications Laboratories are involved in programs and activities relevant to audio/video: Eindhoven, the Netherlands (TV, monitors and radio/audio); Hamburg, Germany (TV and radio/audio); Southampton, UK (teletext and digital audio, including CD technology).

They support all audio/video applications and work closely with customers, meeting and often anticipating their needs.

Many key developments have come from Philips laboratories - one-chip TV signal processors, ICs for memory-based TV features, a TV microcontroller with on-chip teletext, a two-chip receiver module for car radio, and a one-chip self-tuned radio are just a few examples. In addition, there are also Product Development groups in all the above locations.

#### **Partnership**

Since the spur for many of the ICs and discrete semiconductors in this databook have come from a cross-fertilisation of ideas with customers, we are fully aware that we need to be not only semiconductor suppliers, but also partners who are willing to work with customers to find solutions and help keep them at the leading edge of their field. At Philips Semiconductors, we work very closely with our audio/video customers and are determined to maintain a reputation for being the world's most customer-oriented supplier.

#### WHAT THIS BOOK AND CD-ROM CONTAIN

This book is a supplement to the existing databook IC01 - Semiconductors for radio and audio, and contains abstracts of our latest datasheets. In addition, all the datasheets found in IC01 and this supplement are contained on the accompanying CD-ROM. The datasheet files on the CD-ROM are in Adobe's Portable Document Format (PDF) - a cross-platform file format that requires Acrobat Reader to view (we have also supplied Acrobat Reader on the CD-ROM). Acrobat Reader enables you to view and print pages, and perform basic searches. Please refer to the READ.ME file on the CD-ROM for information on the CD's contents and organization, as well as instructions how to install and use Acrobat Reader.

#### FOR MORE INFORMATION

Although the information in this databook is up-to-date at the time of going to press, the world of audio/video is so fast moving it is possible that some very recent developments may not have made it into this edition. For the latest information contact your local Philips organization (see the back page of this databook for addresses), or visit our Internet home page at: http://www.semiconductors.philips.com/ps/

# **SELECTION GUIDES**

|                    |  |   | Page |

|--------------------|--|---|------|

| Functional index   |  | 0 | 6    |

| Alphanumeric index |  |   | 13   |

| Renlacement list   |  |   | 16   |

**Functional index**

|                        |                                                        | PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RADIO RECEIVERS        |                                                        | . AGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                        |                                                        | Angry Johnson (1967).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AM/FM receivers        |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                        |                                                        | e de la companya della companya della companya de la companya della companya dell |

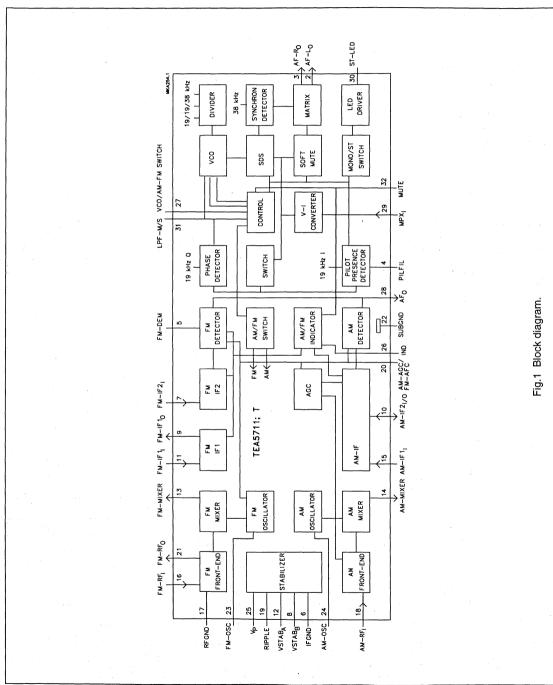

| TEA5711; TEA5711T      | AM/FM radio receiver circuit                           | 349                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

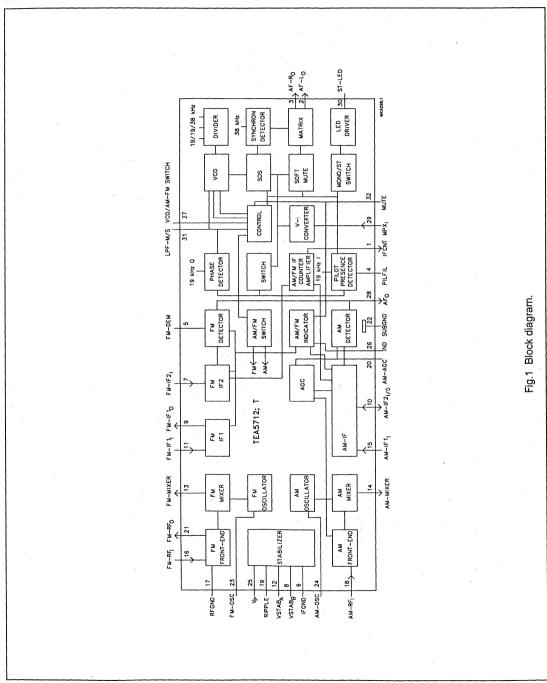

| TEA5712; TEA5712T      | AM/FM stereo DTS radio circuit                         | 352                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TEA5757; TEA5759       | Self tuned radio (STR)                                 | 357                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

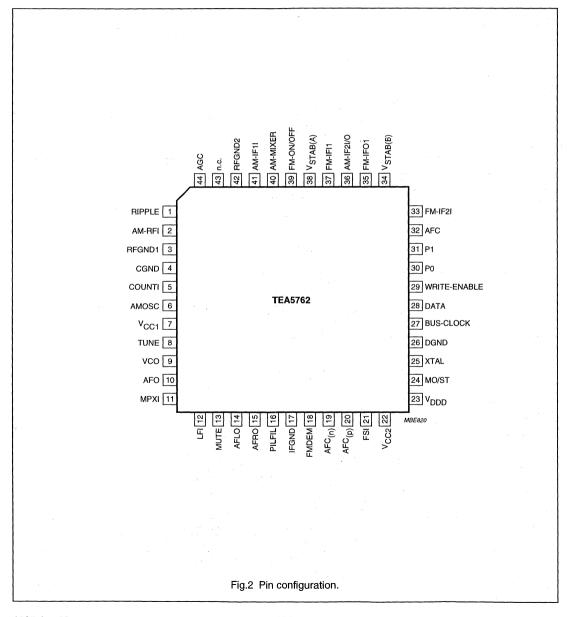

| TEA5762                | Self tuned radio                                       | 362                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                        |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FM receivers           |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                        |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

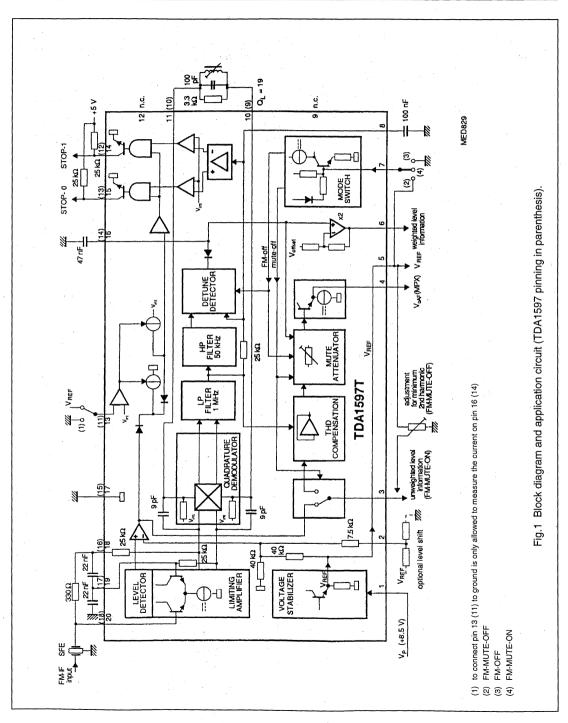

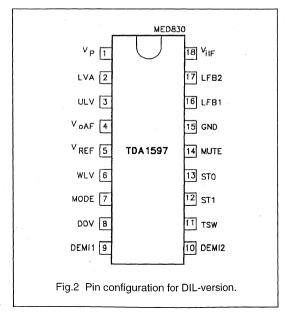

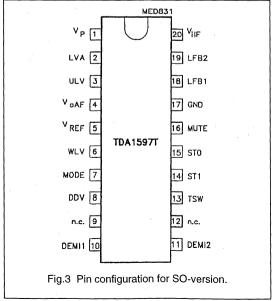

| TDA1597                | IF amplifier/demodulator for FM radio receivers        | 286                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TDA1599                | IF amplifier/demodulator for FM radio receivers        | 289                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DAGO (Duratistan Adlas | and Ohammal Oalaatinita)                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PACS (Precision Adjac  | ent Channel Selectivity)                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

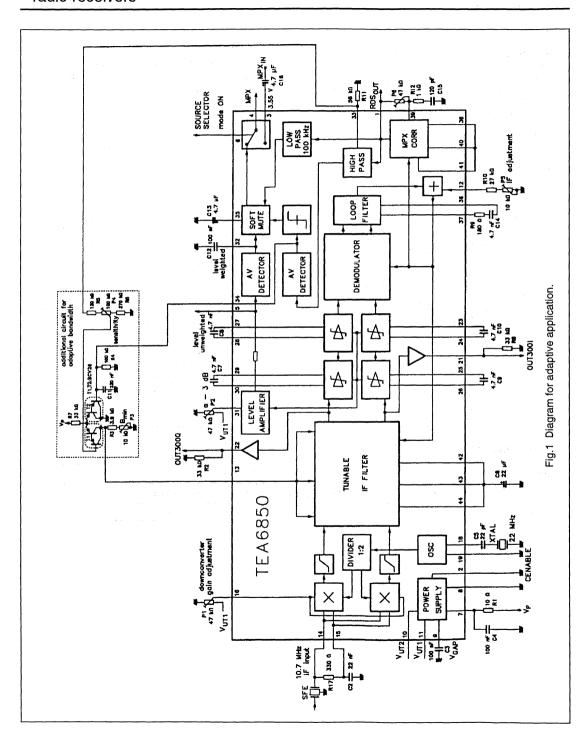

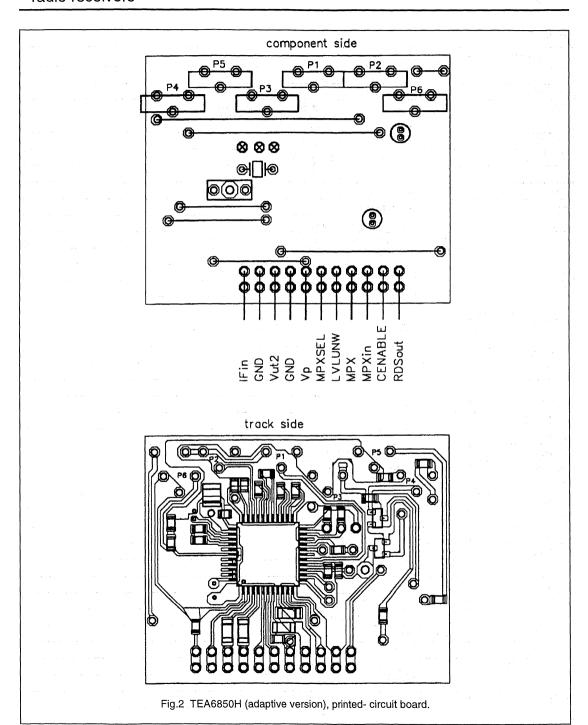

| TEA6850                | IF filter/amplifier/demodulator for FM radio receivers | 397                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Combination AM/FM. IF  | F, PLL, MPX and NC circuits                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| oombination / m./ m, n | , 1 = 1, IIII X and 110 should                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

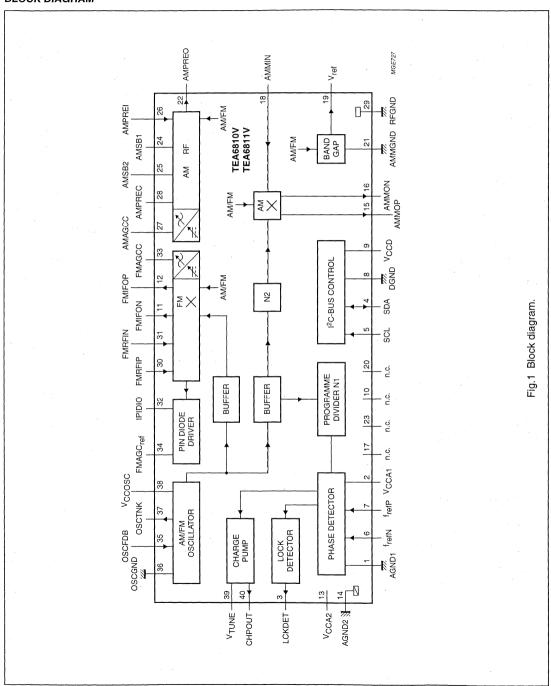

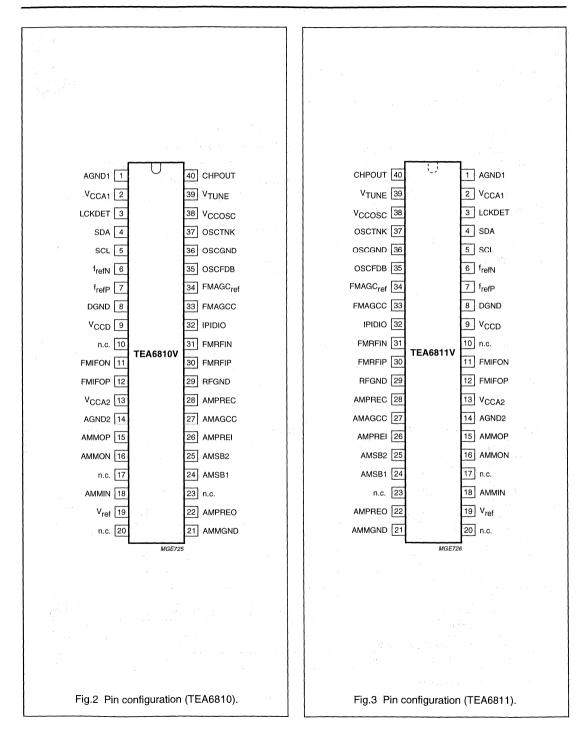

| TEA6810V; TEA6811V     | Front-end and PLL synthesizer for car radios           | 381                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

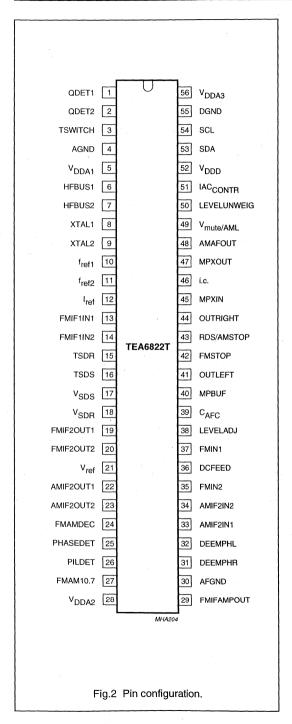

| TEA6821T               | ICE car radio                                          | 386                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TEA6822T               | In Car Entertainment (ICE) car radio                   | 392                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                        |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Frequency/voltage syn  | thesizers                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                        |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TDA8735                | PLL frequency synthesizer                              | 346                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

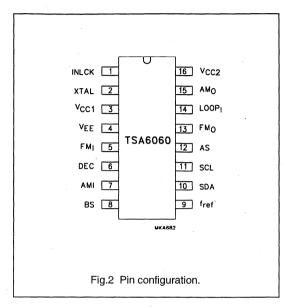

| TSA6060                | Fast radio tuning PLL frequency synthesizer            | 401                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Stereo decoders and N  | oise supPression circuits                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Stereo decoders and it | oise suprifession circuits                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

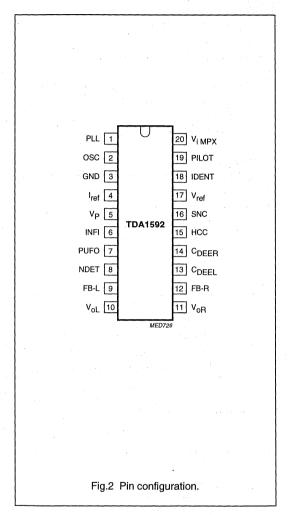

| TDA1592                | PLL stereo decoder and noise blanker                   | 283                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TEA5711; TEA5711T      | AM/FM radio receiver circuit                           | 349                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TEA5712; TEA5712T      | AM/FM stereo DTS radio circuit                         | 352                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |